Spis Treści

- Streszczenie: Giga-Skalowanie Pakowania na Czołowej Pozycji

- Krajobraz Rynku i Kluczowi Gracze w 2025 Roku

- Przełomowe Technologie w Giga-Skalowym Pakowaniu IC

- Zaawansowane Materiały i Innowacje Produkcyjne

- Trendy Integracji: Chiplety, 3D i Heterogeniczne Pakowanie

- Globalne Wyzwania i Możliwości Łańcucha Dostaw

- Regulacje, Środowisko i Przegląd Standardów Branżowych

- Prognozy Rynkowe i Perspektywy Inwestycyjne do 2029 Roku

- Analiza Konkurencyjna: Strategie Kluczowych Firm (np. intel.com, tsmc.com, amkor.com)

- Perspektywy Przyszłości: Wschodzące Aplikacje i Długoterminowe Trendy

- Źródła i Odesłania

Streszczenie: Giga-Skalowanie Pakowania na Czołowej Pozycji

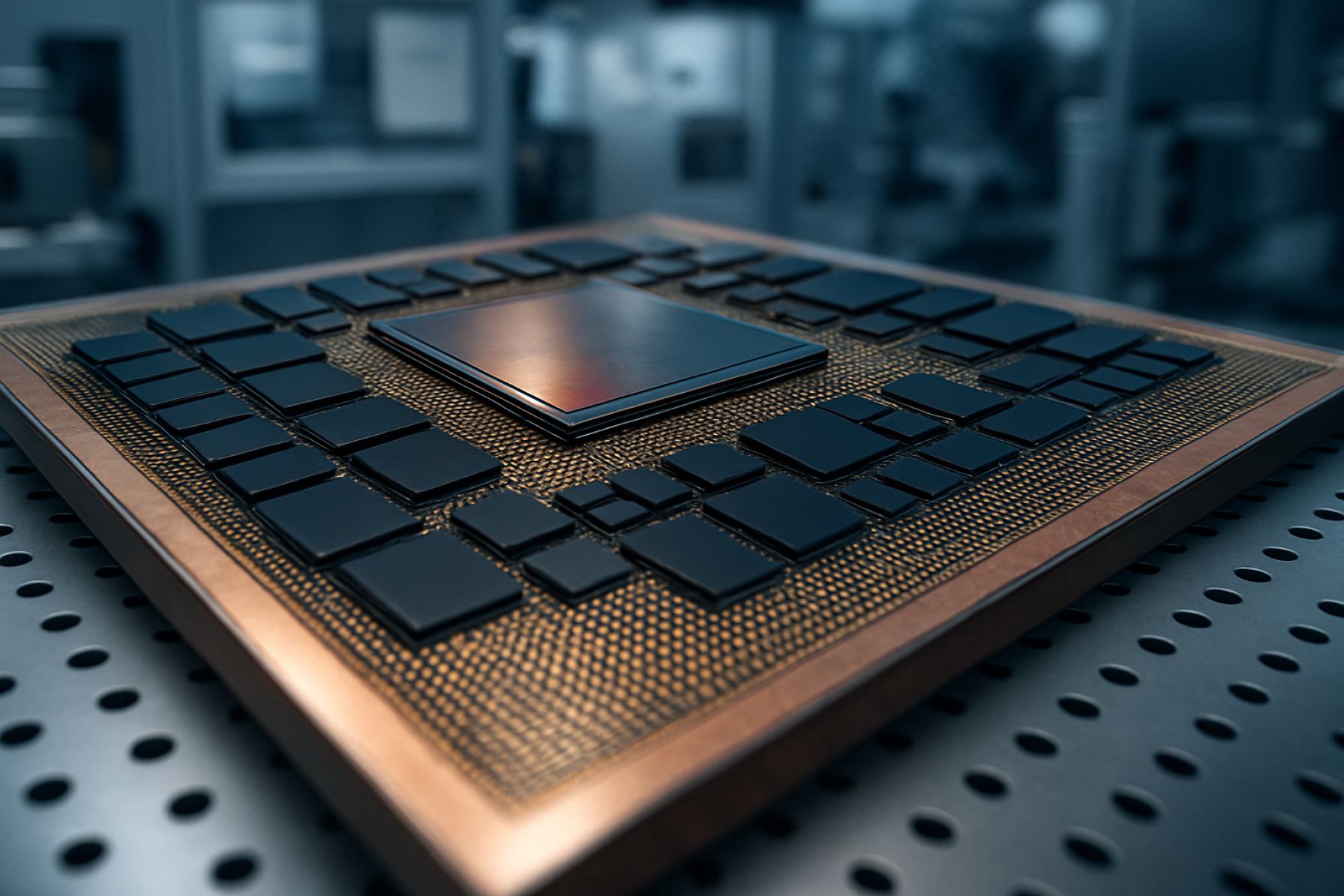

Ewolucja rozwiązań pakowania układów scalonych (IC) w skali giga szybko przekształca krajobraz półprzewodników, umieszczając zaawansowane technologie pakowania w czołówce innowacji na rok 2025 i dalej. W miarę jak złożoność urządzeń oraz liczby tranzystorów wzrastają do setek miliardów, tradycyjne monolityczne skalowanie napotyka ograniczenia fizyczne i ekonomiczne. W odpowiedzi branża półprzewodnikowa przyspiesza inwestycje w nowe architektury pakowania — takie jak integracja 2.5D/3D, projektowanie oparte na chipletach oraz zaawansowane technologie podłoży — aby sprostać wyzwaniom wydajności, mocy i plonów związanym z integracją w skali giga.

Wiodące firmy napędzają tę transformację poprzez znaczące ogłoszenia i kamienie milowe w harmonogramie. TSMC wciąż rozwija swoje platformy System on Integrated Chips (SoIC) i CoWoS (Chip-on-Wafer-on-Substrate), umożliwiając wysoką gęstość stosów 3D oraz integrację wielu układów dla aplikacji AI, wysokowydajnego obliczania (HPC) i centrów danych. W 2025 roku rozwiązania CoWoS i SoIC następnej generacji TSMC będą gotowe do produkcji na dużą skalę, wspierając architektury chipletowe i zwiększając gęstości połączeń daleko poza 2000 I/O na mm². Podobnie, Intel rozwija swoje technologie stosowania 3D Foveros i EMIB (Embedded Multi-die Interconnect Bridge), z masową produkcją Meteor Lake oraz przyszłych akceleratorów AI wykorzystujących te możliwości pakowania w skali giga.

Na froncie materiałów i podłoży ASE Technology Holding, największy na świecie zewnętrzny dostawca półprzewodnikowych usług montażowych i testowych (OSAT), zwiększa swoje możliwości Fan-Out Wafer-Level Packaging (FOWLP) oraz 2.5D/3D, koncentrując się na ultracienkich warstwach redystrybucji (RDL) i zaawansowanych podłożach, aby dostosować się do integracji chipów w skali giga. W międzyczasie Amkor Technology rozwija swoje linie System-in-Package (SiP) o wysokiej gęstości i fan-out o wysokiej gęstości (HDFO), celując w rynki AI i szybkich sieci, w których pakowanie w skali giga jest kluczowe dla przepustowości i efektywności energetycznej.

Organizacje branżowe, takie jak SEMI oraz JEDEC, aktywnie publikują nowe standardy i plany rozwoju, odzwierciedlając przesunięcie w kierunku heterogenicznej integracji i pakowania w skali giga. Te standardy mają na celu zapewnienie interoperacyjności i niezawodności w coraz bardziej złożonych systemach bazujących na wielu układach i chipletach.

Patrząc w przyszłość, rozwiązania pakowania IC w skali giga mają wspierać nową falę innowacji w AI, HPC i zaawansowanych urządzeniach mobilnych. Z inwestycjami wartymi miliardy dolarów i silną zgodą w branży co do heterogenicznej integracji, okres 2025–2027 prawdopodobnie przyniesie nową erę, w której zaawansowane pakowanie, a nie tylko skalowanie tranzystorów, stanie się głównym czynnikiem umożliwiającym wydajność półprzewodników i różnicowanie systemów.

Krajobraz Rynku i Kluczowi Gracze w 2025 Roku

Krajobraz rynku dla rozwiązań pakowania układów scalonych (IC) w skali giga w 2025 roku charakteryzuje się szybkim postępem, zażartą konkurencją i intensywnym skupieniem na heterogenicznej integracji, technologiach systemów w pakiecie (SiP) oraz zaawansowanych materiałach podłoży. W miarę jak producenci półprzewodników dążą do osiągnięcia węzła poniżej 2nm, pakowanie stało się kluczowym czynnikiem umożliwiającym wydajność urządzeń, efektywność energetyczną i redukcję formy, co prowadzi do znaczących inwestycji i współpracy w całym łańcuchu dostaw.

Wiodące fabryki półprzewodnikowe i zewnętrzni dostawcy usług montażowych i testowych (OSAT) znajdują się na czołowej pozycji w innowacjach pakowania w skali giga. TSMC nadal dominuje dzięki swojej platformie 3D Fabric, która integruje zaawansowane technologie chipletów i pakowania wafer-on-wafer, w tym technologie CoWoS (Chip-on-Wafer-on-Substrate) i SoIC (System-on-Integrated-Chips). W 2025 roku TSMC zwiększa swoją zdolność do produkcji CoWoS w celu wsparcia pamięci o wysokiej przepustowości (HBM) oraz zaawansowanych aplikacji AI, co widać w ostatnich rozszerzeniach w swoim zakładzie w Zhunan. Samsung Electronics również intensywnie inwestuje w swoje oferty X-Cube (3D-IC) oraz I-Cube (2.5D/3D SiP), celując w integrację w skali giga dla procesorów centrum danych następnej generacji oraz HPC.

Tymczasem Intel Corporation wykorzystuje swoje technologie EMIB (Embedded Multi-die Interconnect Bridge) oraz Foveros 3D, planując zwiększenie produkcji takich akceleratorów obliczeniowych i AI w 2025 roku. Harmonogram zaawansowanego pakowania firmy, podkreślony na ostatnich wydarzeniach branżowych, wskazuje na przejście w kierunku zintegrowanych platform łączących układy logiczne, pamięci i I/O w jednym pakiecie.

Wśród OSAT-ów ASE Technology Holding oraz Amkor Technology zwiększają zdolności produkcyjne dla SiP, fan-out wafer level packaging (FOWLP) oraz integracji 2.5D/3D. Platforma VIPack ASE i technologie HDFO oraz SLIM/SWIFT Amkora są przyjmowane dla zaawansowanych aplikacji w AI, motoryzacji oraz elektronice konsumpcyjnej, przy czym obie firmy ogłosiły rozszerzenia obiektów oraz strategiczne partnerstwa w Azji i USA.

Dostawcy materiałów i podłoży, tacy jak IBIDEN Co., Ltd. i SHINKO ELECTRIC INDUSTRIES CO., LTD., są kluczowi dla ekosystemu, dostarczając wysokogęste organiczne podłoża i interposerów wymaganych do pakowania w skali giga. Ich inwestycje w technologie produkcyjne i zdolności są kluczowe dla zaspokojenia prognozowanego wzrostu popytu do 2025 roku i później.

Patrząc w przyszłość, sektor pakowania IC w skali giga jest gotowy na trwały wzrost, napędzany proliferacją zadań AI, architektur chipletów i pamięci następnej generacji. Zbieżność wiodących fabryk, OSAT-ów i dostawców materiałów będzie nadal definiować krajobraz konkurencyjny, a rok 2025 będzie oznaczał kluczowy moment dla wprowadzenia technologii i dostosowania udziału w rynku.

Przełomowe Technologie w Giga-Skalowym Pakowaniu IC

Giga-skalowe pakowanie układów scalonych (IC), definiowane przez agregację dziesiątek miliardów tranzystorów i chipletów w zintegrowane systemy, wkracza w fazę szybkich innowacji w 2025 roku. Sprostać wymaganiom wydajności, mocy i gęstości zaawansowanych węzłów napędza przełomy w rozwiązaniach pakowania, takich jak integracja 2.5D i 3D, pakowanie na poziomie wafer i zaawansowane technologie podłoży.

Jednym z najbardziej widocznych przełomów jest integracja heterogeniczna, gdzie wiele chipletów wykonanych w różnych technologiach procesowych jest łączonych w jednym pakiecie. Intel Corporation przyspieszył wdrażanie swoich technologii EMIB (Embedded Multi-die Interconnect Bridge) i Foveros 3D, umożliwiając wysokoprzepustowe połączenia i wertykalne stosowanie logiki i pamięci dla produktów, które mają przekroczyć 100 miliardów tranzystorów w nadchodzących latach. W 2025 roku roadmapa Intela przewiduje agresywne rozszerzenie Foveros Direct, umożliwiające bezpośrednie połączenie miedzi z miedzią przy mniejszych odległościach dla wsparcia integracji w skali giga.

Podobnie, Tajwańska Firma Półprzewodnikowa (TSMC) rozwija swoją platformę 3DFabric, łącząc CoWoS (Chip-on-Wafer-on-Substrate) oraz SoIC (System on Integrated Chips) dla dużej integracji logiki z pamięcią. CoWoS-L TSMC, wprowadzony dla wysokowydajnego obliczania (HPC) i akceleratorów AI, wspiera interposery o rozmiarach retikula przekraczających 2500mm2, istotne dla zastosowań w skali giga. Roadmapa firmy na rok 2025 kładzie nacisk na większą przepustowość, niższe opóźnienia i mniejsze rozstawy wypustek, kluczowe dla integracji dziesiątek chipletów w jednym pakiecie.

Technologia podłoża o wysokiej gęstości również szybko ewoluuje. Samsung Electronics przekracza granice z rozwiązaniami H-Cube i X-Cube, które pozwalają na stosowanie i połączenie wielu dies z mikrowypustkami i hybrydowym łączeniem. Technologie te są przyjmowane dla chipów AI, sieciowych oraz centrów danych, gdzie IC w skali giga stają się standardem.

Równocześnie Advanced Micro Devices (AMD) rozszerzyło swoje zastosowanie architektur opartych na chipletach, wykorzystując zaawansowane pakowanie, aby poprawić wydajność na wat oraz plon. Nowe generacje akceleratorów EPYC i Instinct od AMD, które mają być uruchomione w 2025 roku, demonstrują integrację wielu logik i pamięci za pomocą nowoczesnych organicznych podłoży o wysokiej gęstości i przejrzystych viasach (TSVs).

Patrząc w przyszłość, perspektywy dla pakowania IC w skali giga koncentrują się na współoptymalizacji projektowania, materiałów i produkcji. W miarę jak AI, HPC i obciążenia chmurowe wymagają coraz wyższej integracji, współpraca między foundries, OSAT-ami oraz dostawcami podłoży intensyfikuje się. Gęstość połączeń, zarządzanie termiczne i integracja komponentów optycznych to kluczowe obszary trwających badań, które przygotowują grunt do następnej generacji rozwiązań systemów w pakiecie w skali giga.

Zaawansowane Materiały i Innowacje Produkcyjne

Era giga-skalowych układów scalonych (IC) — gdzie obwody zawierają dziesiątki miliardów tranzystorów — wymaga transformacyjnych postępów w materiałach pakujących i technikach produkcji. W miarę jak złożoność urządzeń i gęstość wzrastają w 2025 roku i później, branża półprzewodnikowa szybko ewoluuje, aby sprostać termicznym, elektrycznym i mechanicznym wyzwaniom związanym z tymi ogromnymi IC.

Kluczywi gracze priorytetowo traktują innowacje podłoży, z organicznymi, szklanymi oraz zaawansowanymi podłożami krzemowymi na czołowej pozycji. AMD i Intel Corporation przyspieszyły przyjęcie wysokogęstych krzemowych interposerów dla architektur chipletów, umożliwiając mniejsze rozstawy połączeń i wyższą przepustowość. Platformy pakowania TSMC System-on-Integrated-Chips (SoIC) i CoWoS (Chip-on-Wafer-on-Substrate) — które już są w produkcji na dużą skalę — są teraz rozszerzane, aby wspierać integrację logiki i pamięci o wysokiej przepustowości, przy czym TSMC raportuje >1000mm² wielkości pakietu i rozstawy połączeń wynoszące do 40μm w swoich najnowszych ofertach.

Zarządzanie termiczne jest istotnym problemem dla IC w skali giga. Samsung Electronics wprowadza zaawansowane materiały termiczne (TIM) oraz wbudowane mikrofluidyczne chłodzenie do swoich linii pakowania 2.5D i 3D, aby skutecznie rozpraszać ciepło. W międzyczasie ASE Technology Holding skomercjalizował podwójnie formowane pakiety z kulistą siatką (DSMBGA) oraz pakowanie na poziomie wafer z fan-out (FOWLP) z wbudowanymi rozpraszaczami ciepła, celując w rynki AI i wysokowydajnego obliczania.

W produkcji trend zmierza w kierunku pakowania na poziomie panelu (PLP) dla większej wydajności i opłacalności. Amkor Technology oraz ASE Technology Holding obie zwiększają zdolności PLP, aby pomieścić wielkości i ilości dies wymagane dla urządzeń w skali giga, przy czym Amkor raportuje znaczące postępy w dużych technologiach warstw redystrybucji (RDL) dla produkcji w 2025 roku.

Postępy materiałowe są równie kluczowe. Shinko Electric Industries i IBIDEN Co., Ltd. innowują w zakresie podłoży o niskich stratach i wysokiej gęstości z poprawionym współczynnikiem rozszerzalności cieplnej (CTE), co jest istotne dla niezawodności w skali giga. Firmy te opracowują szklane podłoża rdzeniowe i nowe organiczne materiały budowlane, których wprowadzenie do łańcucha dostaw przewiduje się w najbliższych latach.

Prognozy na 2025 rok i później sugerują, że pakowanie IC w skali giga będzie coraz bardziej polegać na heterogenicznej integracji, zaawansowanych podłożach oraz nowoczesnym chłodzeniu. Współpraca między fabrykami, OSAT-ami oraz dostawcami podłoży będzie kluczowa w celu zaspokojenia roadmapy skalowania branży i celów wydajnościowych.

Trendy Integracji: Chiplety, 3D i Heterogeniczne Pakowanie

Przejście na pakowanie układów scalonych w skali giga jest zasadniczo kształtowane przez zaawansowane technologie integracji — wśród nich architektury chipletów, integracja 3D oraz heterogeniczne pakowanie. W miarę jak producenci półprzewodników starają się sprostać wymaganiom związanym ze sztuczną inteligencją, wysokowydajnym obliczaniem oraz aplikacjami centrów danych, podejścia te szybko się rozwijają i są przyjmowane w komercyjnych produktach do 2025 roku i później.

Projektowanie oparte na chipletach umożliwia projektantom obejście ograniczeń dotyczących plonów i skalowania monolitycznych dies poprzez podział złożonych systemów na mniejsze, funkcjonalnie specyficzne chiplety. To modułowe podejście pozwala na integrację logiki, pamięci, analogowych i funkcji I/O przy optymalnych węzłach procesowych dla każdej funkcji. Advanced Micro Devices, Inc. (AMD) udowodniło wykonalność tej architektury w produktach takich jak rodziny EPYC i Ryzen, potwierdzając jednocześnie kontynuację rozwoju następnej generacji procesorów i GPU opartych na chipletach planowanych na 2025 rok i później.

Integracja trójwymiarowa (3D) dodatkowo zwiększa gęstość funkcjonalną poprzez wertykalne stawianie wielu dies, połączonych za pomocą zaawansowanych przejrzystych viasów (TSVs) lub hybrydowego łączenia. Tajwańska Firma Półprzewodnikowa (TSMC) rozwija swoją platformę 3DFabric, w tym rozwiązania SoIC (System on Integrated Chips) oraz CoWoS (Chip-on-Wafer-on-Substrate), aby wspierać projekty w skali giga. Na początku 2025 roku TSMC zwiększa produkcję masową modułów CoWoS z rozmiarami podłoży przekraczającymi 3000 mm2, aby sprostać wymaganiom akceleratorów AI generatywnej oraz dużych silników wnioskowania.

Integracja heterogeniczna łączy chiplety, stosy pamięci i wyspecjalizowane akceleratory — mogące być wykonane w różnych węzłach procesowych i materiałach — w jednym pakiecie. Intel Corporation komercjalizuje swoją technologię Foveros Direct, umożliwiającą łączenie hybrydowe o wąskich rozstawach dla stawiania logiki na logice. Umożliwia to elastyczne konfiguracje systemów oraz optymalizację mocy/wydajności przy złożoności w skali giga. Samsung Electronics Co., Ltd. również inwestuje w platformy X-Cube i I-Cube, celując w AI, pamięć o wysokiej przepustowości oraz następne generacje mobilnych SoC.

Patrząc w przyszłość, rozwiązania pakowania w skali giga mają przyspieszyć adopcję, napędzaną potrzebą integracji bilionów tranzystorów w koncentrowanych danych i obciążeniach AI. Konsorcja branżowe, takie jak ASE Technology Holding Co., Ltd., pracują nad standaryzacją interfejsów chipletowych, interposerów i sieci dostarczania energii, aby wspierać interoperacyjność ekosystemu. Sektor oczekuje znaczących postępów w produkcji podłoży, zarządzaniu termicznym oraz narzędziach współprojektowania, które będą wspierać integrację w skali giga do końca dekady.

Globalne Wyzwania i Możliwości Łańcucha Dostaw

Szybki rozwój technologii pakowania układów scalonych (IC) w skali giga — takich jak zaawansowane 2.5D/3D IC, chiplety i integracja heterogeniczna — zasadniczo przekształca dynamikę globalnego łańcucha dostaw w 2025 roku i później. W miarę jak branża półprzewodnikowa dąży do zaspokojenia rosnącego popytu na wysokowydajne obliczenie, akceleratory AI i sieci następnej generacji, złożoność i skala rozwiązań pakowania pojawiły się jako intensywne zarówno wyzwania, jak i możliwości w całym łańcuchu wartości.

Jednym z głównych wyzwań jest odporność łańcucha dostaw. Wysoce wyspecjalizowane sprzęty, materiały (np. wysokogęste podłoża, zaawansowane podkładki), oraz precyzyjne kontrole procesów wymagane do pakowania w skali giga koncentrują ryzyko w wąskiej grupie dostawców. Na przykład TSMC i Intel rozszerzyły swoje zaawansowane zdolności pakowania, ale globalne niedobory podłoży i lokalne zakłócenia (np. napięcia geopolityczne, wąskie gardła logistyczne) pozostają istotnymi kwestiami. Aby złagodzić te problemy, wiodące firmy inwestują w dywersyfikację geograficzną i podwójne źródła dla krytycznych materiałów i narzędzi.

Jednocześnie przejście na architektury chipletowe i integrację heterogeniczną stwarza nowe możliwości dla modułowej współpracy w łańcuchu dostaw. Przyjęcie chipletów przez AMD w swoich procesorach EPYC i Ryzen dowodzi, jak standardowe interfejsy i otwarte połączenia die-do-die mogą umożliwić bardziej elastyczne źródła i szybsze cykle innowacji. Konsorcja, takie jak Universa Chiplet Interconnect Express (UCIe), których członkowie założyciele to Intel, AMD, TSMC i Samsung Electronics, przyspieszają branżowe przyjęcie interoperacyjnych rozwiązań, obniżając bariery wejścia dla nowych uczestników ekosystemu.

Po stronie produkcji prowadzone są inwestycje w rozbudowę zdolności. TSMC zwiększa swoje linie pakowania CoWoS i SoIC, celując zarówno w zwiększenie wydajności, jak i mniejsze rozstawy połączeń w celu wsparcia chipów AI i HPC. Intel zwiększa swoje możliwości w zakresie technologii Foveros Direct oraz EMIB, a Samsung Electronics skomercjalizował swoją platformę X-Cube 3D. Ruchy te sygnalizują globalny wyścig o zapewnienie liderstwa w pakowaniu w skali giga, wymagając dużych zobowiązań kapitałowych dla podłoży, narzędzi i automatyzacji.

Patrząc na najbliższe lata, outlook dla rozwiązań pakowania IC w skali giga zależy od równoważenia odporności łańcucha dostaw z prędkością innowacji. Współprace w zakresie standardów, regionalne inwestycje w zaawansowaną infrastrukturę pakowania oraz cyfryzacja łańcucha dostaw (śledzenie, analityka predykcyjna) będą kluczowe dla zarządzania ryzykami i uchwycenia pojawiających się możliwości rynkowych. W miarę jak rynki końcowe dla chipów AI, motoryzacyjnych i centrów danych rosną, ekosystem prawdopodobnie zobaczy ścisłą integrację między foundries, OSAT-ami, dostawcami podłoży oraz dostawcami narzędzi EDA, przekształcając tradycyjne granice łańcucha dostaw półprzewodników.

Regulacje, Środowisko i Przegląd Standardów Branżowych

Szybka ewolucja rozwiązań pakowania układów scalonych (IC) w skali giga prowadzi do znacznych zmian w regulacjach, środowisku i standardach przemysłowych, gdy poruszamy się w kierunku 2025 roku i później. W miarę jak złożoność IC wzrasta — oznaczona przez zaawansowane węzły, zwiększoną integrację chipletów oraz heterogeniczne pakowanie — organy regulacyjne oraz konsorcja branżowe aktualizują ramy, aby sprostać nowym wyzwaniom związanym z bezpieczeństwem, zrównoważonym rozwojem oraz interoperacyjnością.

Regulacje dotyczące środowiska pozostają w centrum uwagi, ponieważ procesy pakowania w skali giga wymagają większej uwagi do zarządzania materiałami i wpływów cyklu życia. Dyrektywa Unii Europejskiej o Ograniczeniu Stosowania Niebezpiecznych Substancji (RoHS) nadal kształtuje wybory materiałowe, zmuszając producentów do stosowania opakowań wolnych od ołowiu i halogenów. W międzyczasie branża mierzy się z europejską Zieloną Umową i strategiami gospodarki o obiegu zamkniętym, wprowadzając innowacje w zakresie materiałów podłoży nadających się do recyklingu oraz procesów produkcyjnych o niskiej emisji. Na przykład, Infineon Technologies AG podkreślił swoje zobowiązanie do redukcji wpływu na środowisko poprzez energooszczędną produkcję i wykorzystanie materiałów z odzysku w swoich zaawansowanych pakietach IC.

W Ameryce Północnej i Azji, uzgodnienie regulacyjne postrzegane jest jako kluczowe dla odporności łańcucha dostaw oraz globalnego dostępu do rynku. Organizacje takie jak SEMI oraz Stowarzyszenie Technologii Półprzewodników JEDEC współpracują z producentami w celu zharmonizowania standardów pakowania, koncentrując się na niezawodności, zarządzaniu termicznym oraz wydajności elektrycznej, w miarę jak gęstości IC rosną. Ostatnio zaktualizowane standardy JEDEC dla zaawansowanego pakowania określają wymogi dotyczące rozwiązań w skali giga, w tym rozmiaru podłoża, dostarczania energii i integralności sygnału, zapewniając kompatybilność między dostawcami i wspierając szybki rozwój ekosystemu.

Branża przyspiesza także przyjęcie ram związanych z zrównoważonym rozwojem i transparentnością. Intel Corporation zobowiązał się do osiągnięcia zerowej emisji gazów cieplarnianych w swoich globalnych operacjach do 2040 roku, co obejmuje optymalizację procesów pakowania i materiałów do urządzeń w skali giga. Podobnie, Tajwańska Firma Półprzewodnikowa (TSMC) publikuje coroczne raporty dotyczące zrównoważonego rozwoju, w których szczegółowo opisuje redukcję zużycia wody i chemikaliów w swoich zaawansowanych zakładach pakowania — co staje się coraz ważniejszym czynnikiem w miarę jak rozwiązania w skali giga wymagają bardziej zasobożernych procesów.

Patrząc w przyszłość, przewiduje się, że krajobraz regulacyjny będzie się zaostrzał, gdy rządy i organy branżowe wprowadzą surowsze wymogi dotyczące oceny cyklu życia, ujawnienia emisji węgla oraz bezpieczeństwa materiałów w pakowaniu IC w skali giga. Te rozwijające się ramy będą kształtować inwestycje i innowacje, zmuszając producentów do równoważenia wymagań dotyczących wydajności z zrównoważonym rozwojem i zgodnością, w miarę jak branża zbliża się do ery eksaskali.

Prognozy Rynkowe i Perspektywy Inwestycyjne do 2029 Roku

Rynek rozwiązań pakowania układów scalonych (IC) w skali giga jest gotowy na dynamiczny rozwój do 2029 roku, napędzany rosnącym popytem na wysokowydajne obliczenia, sztuczną inteligencję, centra danych i zaawansowane urządzenia mobilne. Pakowanie w skali giga — obejmujące technologie zdolne do wspierania miliardów tranzystorów i ultra-wysokiej gęstości I/O — wymaga innowacji w materiałach, projektowaniu oraz produkcji, prowadząc do znaczących wydatków kapitałowych i strategicznych inwestycji ze strony liderów branżowych.

Od 2025 roku główni producenci półprzewodników szybko zwiększają swoje możliwości pakowania zaawansowanego. Tajwańska Firma Półprzewodnikowa (TSMC) ogłosiła agresywne kamienie milowe w planie rozwoju dla technologii System-on-Integrated-Chips (SoIC) i 3D fabric, z masową produkcją zaawansowanych rozwiązań CoWoS i opartych na chipletach, która ma się podwoić do 2026 roku. TSMC inwestuje ponad 40 miliardów dolarów w nowe zakłady i badania oraz rozwój, aby wspierać skalowanie platform dla pamięci o wysokiej przepustowości (HBM) i akceleratorów AI.

Intel Corporation przyspiesza wdrażanie platformy pakowania 3D Foveros, z planowanym zwiększeniem produkcji w latach 2025-2026. Ostatnie inwestycje firmy — przekraczające 20 miliardów dolarów w nowe fabryki i zakłady pakowania w USA oraz Europie — mają na celu zabezpieczenie pozycji lidera w heterogenicznej integracji na dużą skalę oraz umożliwienie produktów serwerowych, sieciowych i AI nowej generacji.

Samsung Electronics zwiększa swoje oferty X-Cube (integracja 3D) oraz H-Cube (integracja heterogeniczna), inwestując miliardy dolarów w badania i rozwój pakowania oraz linie produkcyjne. Samsung przewiduje podwojenie popytu na rozwiązania pakowania w skali giga w wysokowydajnej pamięci i układach logicznych do 2027 roku, podkreślając swoją współpracę z dostawcami usług chmurowych oraz deweloperami chipów AI.

Globalna zmiana w kierunku architektur chipletowych dodatkowo przyspiesza inwestycje w dużą produkcję podłoża i zaawansowane połączenia. Amkor Technology, jeden z wiodących dostawców zewnętrznych usług montażowych i testowych (OSAT), ogłosił nowe zakłady w Wietnamie i Portugalii, celując w fan-out o wysokiej gęstości oraz pakowanie 2.5D/3D dla projektów w skali giga, z przewidywaną zdolnością operacyjną mającą ruszyć do 2026 roku.

Patrząc w kierunku 2029 roku, organizacje branżowe, takie jak SEMI, prognozują dwucyfrowe roczne stopy wzrostu (CAGR) dla zaawansowanego pakowania, gdzie rozwiązania w skali giga będą stanowić coraz większy rynek całkowity oraz inwestycje kapitałowe. Kluczowe czynniki to proliferacja zadań AI, obliczenia eksaskalne oraz przejście na węzły procesowe poniżej 2nm, które wszystkie wymagają zaawansowanego pakowania w celu optymalizacji mocy, wydajności i formy.

Analiza Konkurencyjna: Strategie Kluczowych Firm (np. intel.com, tsmc.com, amkor.com)

Globalny wyścig o rozwiązania pakowania układów scalonych (IC) w skali giga intensyfikuje się, gdy producenci półprzewodników i dostawcy zaawansowanego pakowania dążą do innowacji, aby sprostać wymaganiom wyższej wydajności, integracji i efektywności energetycznej. W 2025 roku i w niedalekiej przyszłości liderzy branży wdrażają różnorodne strategie — od własnych architektur pakowania po strategiczne rozszerzenia zdolności — aby zdobyć udział w szybko rozwijającym się rynku IC w skali giga.

Intel Corporation wykorzystuje swoje zaawansowane portfolio pakowania, w tym technologie Foveros oraz EMIB (Embedded Multi-die Interconnect Bridge), aby umożliwić wysoką gęstość, heterogeniczną integrację chipletów dla centrów danych, AI oraz obliczeń klienckich. Firma niedawno ogłosiła duże rozszerzenia swoich zaawansowanych zdolności pakowania w Stanach Zjednoczonych i Europie, przy czym obiekt w Ohio ma wspierać produkcję pakowania w skali giga do połowy dekady. Roadmapa Intela na 2025 rok kładzie nacisk na podejście „foundry systemów”, integrując zaawansowane pakowanie jako kluczowy wyróżnik strategii IDM 2.0 oraz współpracując z partnerami ekosystemowymi, aby umożliwić otwartą interoperacyjność chipletów poprzez standard UCIe (Universal Chiplet Interconnect Express).

TSMC, wiodąca fabryka typu pure-play, nadal rozwija swoje własne platformy CoWoS (Chip-on-Wafer-on-Substrate) oraz InFO (Integrated Fan-Out), które są kluczowe dla IC w skali giga zasilających wysokowydajne obliczenia, sieci oraz akceleratory AI. W 2025 roku TSMC zwiększa swoją zdolność CoWoS, dążąc do podwojenia produkcji w celu zaspokojenia rosnącego zapotrzebowania ze strony hiperskalersów i dostawców chipów AI. Firma inwestuje również w technologie pakowania nowej generacji, takie jak SoIC (System on Integrated Chips), aby umożliwić wertykalne stosowanie układów logicznych i pamięci, co jeszcze bardziej zwiększa gęstość integracji systemu i wydajność. Strategia TSMC koncentruje się na ścisłej współpracy z klientami w celu współoptymalizacji pakowania i węzłów procesowych, co umożliwia szybką adoptację architektur w skali giga.

Amkor Technology, globalny lider w zewnętrznych usługach montażowych i testowych (OSAT), umacnia swoją pozycję poprzez intensywne inwestycje w duże zaawansowane zakłady pakowania, szczególnie w Korei i Wietnamie. Portfolio Amkora obejmuje rozwiązania High-Density Fan-Out, 2.5D/3D IC oraz Silicon Interposer, które są coraz bardziej pożądane dla aplikacji w skali giga w AI, wysokowydajnym obliczaniu i sektorach motoryzacyjnych. W 2024 roku Amkor otworzył swoją największą fabrykę pakowania zaawansowanego w Bac Ninh w Wietnamie, planując zwiększenie zdolności produkcyjnej do 2025 roku i później Amkor Technology. Strategia Amkora kładzie nacisk na odporność łańcucha dostaw, globalny zasięg oraz partnerstwa technologiczne, aby dostarczać skalowalne rozwiązania w skali giga dla zróżnicowanej bazy klientów.

Ogólnie rzecz biorąc, perspektywy dla pakowania IC w skali giga są oznaczone agresywnymi inwestycjami w zdolności, współpracą ekosystemową oraz ciągłymi innowacjami w architekturze pakowania — co pozwala sektorowi na dynamiczny wzrost, gdy popyt na integrację w skali giga przyspiesza przez drugą połowę dekady.

Perspektywy Przyszłości: Wschodzące Aplikacje i Długoterminowe Trendy

W miarę rozwoju branży półprzewodników w kierunku integracji w skali giga — gdzie jednego pakiet może zawierać dziesiątki miliardów tranzystorów i wiele komponentów heterogenicznych — technologia pakowania stała się kluczowym czynnikiem innowacji. W 2025 roku i kolejnych latach perspektywy dla pakowania układów scalonych (IC) w skali giga kształtowane są przez rosnący popyt w obszarze sztucznej inteligencji (AI), wysoko wydajnego obliczania (HPC), zaawansowanego networkingu oraz urządzeń elektronicznych nowej generacji.

Jednym z kluczowych trendów jest szybkie dojrzewanie i skalowanie zaawansowanego pakowania 2.5D i 3D, w tym architektur chipletów. Podejścia te umożliwiają podział dużych dies na mniejsze chiplety, o wysokiej wydajności. Na przykład Intel Corporation wzmocnił swoje technologie EMIB (Embedded Multi-die Interconnect Bridge) oraz Foveros 3D, co pozwala na integrację heterogenicznych chipletów obliczeniowych, pamięci i I/O w jednym pakiecie. Tajwańska Firma Półprzewodnikowa (TSMC) kontynuuje rozwój swoich platform CoWoS (Chip-on-Wafer-on-Substrate) i SoIC (System on Integrated Chips), wspierając coraz większe stosy logiki na logice i logiki na pamięci dla zastosowań w centrach danych oraz akceleratorów AI.

Przewiduje się, że pakowanie w skali giga rozwiąże nie tylko wyzwania związane z gęstością i integracją, ale także z dostarczaniem energii, zarządzaniem termicznym i integralnością sygnału. Advanced Micro Devices, Inc. (AMD) oraz NVIDIA Corporation aktywnie dążą do zaawansowanych rozwiązań GPU i akceleratorów multi-die, wykorzystując wysokowydajne połączenia oraz innowacyjne materiały podłoży, aby sprostać potrzebom generatywnej AI i wydajnego obliczania.

Wschodzące aplikacje, takie jak AI na krawędzi, komunikacja 6G i autonomiczność motoryzacyjna, jeszcze bardziej przyspieszają potrzebę pakowania w skali giga. Na przykład sektor motoryzacyjny wymaga wysoce niezawodnych, termicznie wydajnych i miniaturowanych pakietów IC do fuzji czujników i analizy w czasie rzeczywistym, na co odpowiadają dostawcy tacy jak Infineon Technologies AG oraz Renesas Electronics Corporation.

Patrząc w przyszłość, roadmapy branżowe przewidują dalsze skalowanie rozstawów pomiędzy mikrowypustkami i hybrydowym łączeniem, przyjęcie szklanych podłoży rdzeniowych dla ekstremalnej integralności sygnału oraz proliferację AI-sterowanej automatyzacji projektowania dla złożonych układów pakowania. Działania standaryzacyjne i współprace ekosystemowe — takie jak inicjatywa Universal Chiplet Interconnect Express (UCIe) — mają przyspieszyć interoperacyjność i rozwój ekosystemu (Konsorcjum UCIe).

Podsumowując, rozwiązania pakowania IC w skali giga w 2025 roku i później będą fundamentalnymi czynnikami umożliwiającymi nową generację obliczeń, komunikacji oraz inteligentnych systemów na krawędzi, przy czym innowacje koncentrują się na gęstości, integracji i całościowej wydajności systemu.

Źródła i Odesłania

- Amkor Technology

- JEDEC

- ASE Technology Holding

- IBIDEN Co., Ltd.

- SHINKO ELECTRIC INDUSTRIES CO., LTD.

- Infineon Technologies AG

- Amkor Technology

- NVIDIA Corporation

- Konsorcjum UCIe