Cuprins

- Sumar Executiv: Împachetare Giga-Scale în Prim-Plan

- Peisajul Pieței din 2025 și Jucătorii Cheie

- Tehnologii Revoluționare în Împachetarea IC Giga-Scale

- Materiale Avansate și Inovații în Fabricare

- Tendințe de Integrare: Chiplets, 3D și Împachetare Heterogenă

- Provocări și Oportunități în Lanțul de Aprovizionare Global

- Prezentare Generală a Standardelor Reglementare, de Mediu și Industriale

- Previzionări de Piață și Perspective de Investiții până în 2029

- Analiză Competitivă: Strategiile Companiilor de Vârf (de exemplu, intel.com, tsmc.com, amkor.com)

- Perspective de Viitor: Aplicații Emergente și Tendințe pe Termen Lung

- Surse & Referințe

Sumar Executiv: Împachetare Giga-Scale în Prim-Plan

Evoluția soluțiilor de împachetare a circuitelor integrate (IC) giga-scale transformă rapid peisajul semiconductorilor, plasând tehnologiile avansate de împachetare în fruntea inovației pentru 2025 și nu numai. Pe măsură ce complexitatea dispozitivelor și numărul de tranzistori explodează în sute de miliarde, scalarea monolitică tradițională se confruntă cu constrângeri fizice și economice. Ca răspuns, industria semiconductorilor accelerează investițiile în arhitecturi de împachetare noi — cum ar fi integrarea 2.5D/3D, designul bazat pe chiplet și tehnologiile avansate de substrat — pentru a aborda provocările de performanță, putere și randament în integrarea giga-scale.

Companiile de frunte conduc această transformare cu anunțuri semnificative și repere pe planul de dezvoltare. TSMC continuă să își extindă platformele System on Integrated Chips (SoIC) și CoWoS (Chip-on-Wafer-on-Substrate), permițând stivuirea 3D de mare densitate și integrarea mai multor die pentru aplicații de AI, calcul de înaltă performanță (HPC) și centre de date. În 2025, soluțiile de generație următoare CoWoS și SoIC ale TSMC sunt programate pentru producția în masă, susținând arhitecturi chiplet și depășind densitățile de interconexiune cu mult peste 2.000 I/O pe mm². În mod similar, Intel își avansează tehnologiile de stivuire 3D Foveros și EMIB (Embedded Multi-die Interconnect Bridge), cu producția în masă a Meteor Lake și acceleratoare AI viitoare care valorifică aceste capacități de împachetare giga-scale.

Pe frontul materialelor și substraturilor, ASE Technology Holding, cel mai mare furnizor de asamblare și testare semiconductor extern (OSAT) din lume, își extinde ofertele de Împachetare la Nivel de Wafer (FOWLP) și 2.5D/3D, concentrându-se pe straturi de redistribuție ultra-fine (RDL) și substraturi avansate pentru a facilita integrarea cipurilor în giga-scale. Între timp, Amkor Technology își extinde liniile de sistem în pachet (SiP) de mare densitate și de ventilare în alta densitate (HDFO), vizând piețele AI și rețelistică de mare viteză, unde împachetarea giga-scale este critică pentru banda și eficiența energetică.

Organizațiile din industrie, cum ar fi SEMI și JEDEC, publică activ standarde și hărți de dezvoltare noi, reflectând tranziția către integrarea heterogenă și împachetarea giga-scale. Aceste standarde vizează asigurarea interoperabilității și fiabilității în cadrul unor sisteme din ce în ce mai complexe, bazate pe chiplet și multi-die.

Privind spre viitor, soluțiile de împachetare IC giga-scale sunt așteptate să susțină urm wave de inovație în AI, HPC și dispozitive mobile avansate. Cu investiții de miliarde de dolari și un consens puternic din industrie în jurul integrării heterogene, perioada 2025–2027 va marca cu siguranță o nouă eră în care împachetarea avansată, nu doar scalarea transistorului, devine principalul facilitator pentru performanța semiconductorilor și diferențierea sistemelor.

Peisajul Pieței din 2025 și Jucătorii Cheie

Peisajul pieței pentru soluțiile de împachetare a circuitelor integrate (IC) giga-scale în 2025 este caracterizat prin progrese rapide, competiție acerbă și un accent intensificat pe integrarea heterogenă, tehnologiile sistemului în pachet (SiP) și materialele avansate de substrat. Pe măsură ce producătorii de semiconductori se îndreaptă spre nodurile sub-2nm, împachetarea a devenit un facilitator cheie al performanței dispozitivelor, eficienței energetice și reducerii factorului de formă, determinând investiții semnificative și colaborări în întreaga lanț de aprovizionare.

Furnizorii de semiconductori de top și furnizorii de asamblare și testare semiconductor extern (OSAT) sunt în prim-planul inovației în împachetarea giga-scale. TSMC continuă să domine cu platforma sa 3D Fabric, care integrează împachetarea avansată chiplet și wafer-on-wafer, inclusiv tehnologiile CoWoS (Chip-on-Wafer-on-Substrate) și SoIC (System-on-Integrated-Chips). În 2025, TSMC își va extinde capacitatea CoWoS pentru a sprijini memoriile de mare lățime de bandă (HBM) și aplicațiile avansate de AI, așa cum reiese din expansiunile recente de la instalația sa din Zhunan. Samsung Electronics investește de asemenea masiv în soluțiile sale X-Cube (3D-IC) și I-Cube (2.5D/3D SiP), vizând integrarea giga-scale pentru procecesoarele de centre de date și HPC de generație următoare.

Între timp, Intel Corporation își valorifică tehnologiile EMIB (Embedded Multi-die Interconnect Bridge) și Foveros 3D, având planuri de creștere a producției pentru computere de înaltă performanță și acceleratoare AI în 2025. Harta de dezvoltare a companiei pentru ambalare avansată, evidențiată la evenimente recente din industrie, subliniază o tranziție spre platforme integrate care combină die-uri logice, memorie și I/O într-un singur pachet.

Printre OSAT-uri, ASE Technology Holding și Amkor Technology își extind capacitatea pentru SiP, împachetarea la nivel de wafer cu ventilare de mare densitate (FOWLP) și integrarea 2.5D/3D. Platforma VIPack a ASE și tehnologiile High-Density Fan-Out (HDFO) și SLIM/SWIFT ale Amkor sunt adoptate pentru aplicații avansate în AI, auto și electronice de consum, ambele companii anunțând extinderi de facilități și parteneriate strategice în Asia și SUA.

Furnizorii de materiale și substraturi, cum ar fi IBIDEN Co., Ltd. și SHINKO ELECTRIC INDUSTRIES CO., LTD., sunt cruciali pentru ecosistem, oferind substraturi organice de mare densitate și interpoziții necesare pentru împachetarea giga-scale. Investițiile lor în tehnologia de fabricație și capacitate sunt vitale pentru a satisface creșterea prognozată a cererii până în 2025 și nu numai.

Privind înainte, sectorul de împachetare IC giga-scale este pregătit pentru creștere susținută, stimulată de proliferarea sarcinilor de lucru AI, arhitecturile chiplet și memoria de generație următoare. Convergența celor mai avansate fabrici, OSAT-uri și furnizori de materiale va continua să definească peisajul competitiv, cu 2025 marcând un an crucial pentru desfășurarea tehnologică și realinierea cotei de piață.

Tehnologii Revoluționare în Împachetarea IC Giga-Scale

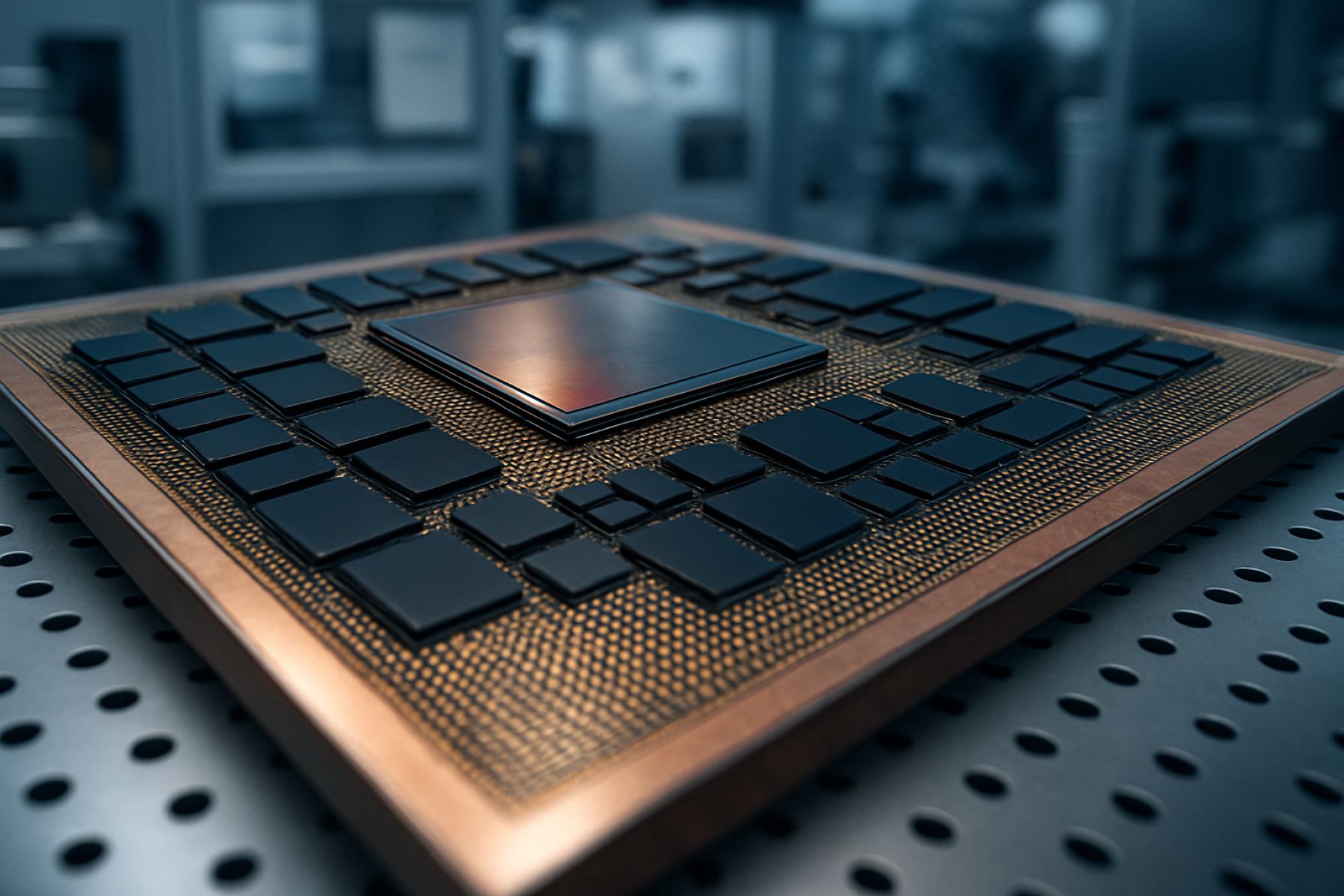

Împachetarea circuitele integrate (IC) giga-scale, definită prin agregarea a zeci de miliarde de tranzistori și chiplet într-un sistem unificat, intră într-o fază de inovare rapidă în 2025. Îndeplinirea cerințelor de performanță, putere și densitate ale nodurilor avansate determină progrese în soluțiile de împachetare cum ar fi integrarea 2.5D și 3D, împachetarea la nivel de wafer și tehnologiile avansate de substrat.

Una dintre cele mai proeminente progrese este integrarea heterogenă, unde mai multe chiplet fabricate cu diverse tehnologii de proces sunt combinate într-un singur pachet. Intel Corporation a accelerat desfășurarea tehnologiilor sale EMIB (Embedded Multi-die Interconnect Bridge) și Foveros 3D, permițând interconexiuni de mare lățime de bandă și stivuirea verticală a logicii și memoriei pentru produse care se așteaptă să depășească 100 de miliarde de tranzistori în anii următori. În 2025, harta de dezvoltare a Intel subliniază extinderea agresivă a Foveros Direct, permițând lipirea directă cu cupru pe cupru la pitch-uri mai fine pentru a sprijini integrarea giga-scale.

În mod similar, Taiwan Semiconductor Manufacturing Company (TSMC) își avansează platforma 3DFabric, combinând CoWoS (Chip-on-Wafer-on-Substrate) și SoIC (System on Integrated Chips) pentru integrarea logică-memorie pe scară largă. CoWoS-L de la TSMC, introdus pentru calcul de înaltă performanță (HPC) și acceleratoare AI, susține interpoziții cu dimensiuni de reticulă ce depășesc 2500mm2, esențiale pentru aplicațiile giga-scale. Harta de dezvoltare a companiei pentru 2025 subliniază lățimi mai mari de bandă, latențe mai mici și pitch-uri ale bump-urilor mai fine, pe care le considerăm esențiale pentru integrarea zecilor de chiplet într-un singur pachet.

Tehnologia substratului de mare densitate evoluează rapid. Samsung Electronics împinge frontierile cu soluțiile sale H-Cube și X-Cube, care permit stivuirea și interconectarea mai multor die cu prințe micro și lipire hibrid. Aceste tehnologii sunt adoptate pentru cipurile AI, de rețelistică și de centre de date acolo unde IC-urile giga-scale devin mainstream.

În paralel, Advanced Micro Devices (AMD) a extins utilizarea arhitecturilor bazate pe chiplet, valorificând împachetarea avansată pentru a îmbunătăți performanța pe watt și randamentul. Acceleratoarele EPYC și Instinct de generație următoare ale AMD, care urmează să fie lansate în 2025, evidențiază integrarea mai multor die-uri logice și de memorie utilizând substraturi organice moderne de mare densitate și prințe prin-silicon (TSV-uri).

Privind înainte, perspectivele pentru împachetarea IC giga-scale sunt centrate pe co-optimizarea designului, materialelor și fabricării. Pe măsură ce sarcinile de lucru AI, HPC și cloud cer integrare din ce în ce mai mare, colaborarea dintre fabrici, OSAT-uri și furnizorii de substraturi se intensifică. Densitatea de interconexiune, gestionarea termică și integrarea componentelor optice sunt domenii cheie de cercetare permanentă, stabilind scena pentru următoarea generație de soluții de sistem în pachet giga-scale.

Materiale Avansate și Inovații în Fabricare

Era circuitelor integrate (IC) giga-scale — în care circuitele conțin zeci de miliarde de tranzistori — necesită progrese transformative în materialele de împachetare și tehnicile de fabricare. Pe măsură ce complexitatea și densitatea dispozitivelor cresc în 2025 și nu numai, industria semiconductorilor evoluează rapid pentru a aborda provocările termice, electrice și mecanice impuse de aceste IC-uri masive.

Jucătorii cheie prioritizează inovațiile în substraturi, cu interpoziții organice, de sticlă și silicona avansată în frunte. AMD și Intel Corporation au accelerat adoptarea interpozițiilor de siliciu de mare densitate pentru arhitecturile chiplet, permițând pitch-uri de interconexiune mai fine și lățimi de bandă mai mari. Platformele de împachetare System-on-Integrated-Chips (SoIC) și CoWoS (Chip-on-Wafer-on-Substrate) ale TSMC — deja în producție în volum mare — sunt acum extinse pentru a sprijini integrarea logică giga-scale și memorie de mare lățime de bandă, TSMC raportând dimensiuni ale pachetelor de >1000mm² și pitch-uri ale interconexiunilor de până la 40μm în cele mai recente oferte.

Gestionarea termică este o preocupare acută pentru IC-urile giga-scale. Samsung Electronics implementează materiale avansate de interfață termică (TIM) și răcire microfluidică integrată în liniile sale de împachetare 2.5D și 3D pentru a dispersa eficient căldura. Între timp, ASE Technology Holding a comercializat grile de bilă moldată pe două fețe (DSMBGA) și împachetare la nivel de wafer cu ventilare (FOWLP) dotate cu distribuitori de căldură integrate, vizând piețele AI și calculul de înaltă performanță.

În fabricare, tendința este spre împachetarea la nivel de panou (PLP) pentru o capacitate mai mare și cost-eficiență. Amkor Technology și ASE Technology Holding își extind atât facilitățile PLP pentru a acomoda dimensiunile die-urilor și volumele necesare pentru dispozitivele giga-scale, cu Amkor raportând progrese semnificative în tehnologia layer-ului de redistribuție de mari dimensiuni (RDL) pentru producția din 2025.

Avansurile în materiale sunt de asemenea cruciale. Shinko Electric Industries și IBIDEN Co., Ltd. inovează substraturi cu pierderi reduse și de mare densitate cu o îmbunătățire a coeficientelor de expansiune termică (CTE) potrivite, esențiale pentru fiabilitatea giga-scale. Aceste companii dezvoltă substraturi cu miez de sticlă și noi construcții organice, care se așteaptă să intre în lanțul de aprovizionare în următorii câțiva ani.

Perspectivele pentru 2025 și dincolo sugerează că împachetarea IC giga-scale va depinde din ce în ce mai mult de integrarea heterogenă, substraturile avansate și răcirea inovatoare. Colaborarea între fabrici, OSAT-uri și furnizorii de substraturi va fi vitală pentru a satisface foaia de parcurs de scalare a industriei și obiectivele de performanță.

Tendințe de Integrare: Chiplets, 3D și Împachetare Heterogenă

Tranziția către împachetarea circuitelor integrate giga-scale este modelată fundamental de tehnologiile avansate de integrare — cele mai importante fiind arhitecturile chiplet, integrarea 3D și împachetarea heterogenă. Pe măsură ce producătorii de semiconductori se străduiesc să răspundă cerințelor de inteligență artificială, calcul de înaltă performanță și aplicații de centre de date, aceste abordări se maturizează rapid și sunt adoptate în produsele comerciale până în 2025 și nu numai.

Designurile bazate pe chiplet permit proiectanților să evite limitările de randament și scalare ale die-urilor monolitice prin împărtirea sistemelor complexe în chiplets mai mici, specifice funcțiilor. Această abordare modulară permite integrarea funcțiilor logice, de memorie, analogice și I/O prin utilizarea nodurilor de proces optimizate pentru fiecare funcție. Advanced Micro Devices, Inc. (AMD) a demonstrat viabilitatea acestei arhitecturi în produse precum familiile EPYC și Ryzen, confirmând dezvoltarea continuării procesoarelor și unităților de procesare grafice (GPU) bazate pe chiplet pentru lansarea în 2025 și peste.

Integrarea în trei dimensiuni (3D) crește densitatea funcțională prin stivuirea mai multor die-uri vertical, interconectate prin prințe hibrid sau prințe prin-silicon (TSV). Taiwan Semiconductor Manufacturing Company Limited (TSMC) își extinde platforma 3DFabric, inclusiv soluțiile SoIC (System on Integrated Chips) și CoWoS (Chip-on-Wafer-on-Substrate), pentru a sprijini designurile giga-scale. La începutul lui 2025, TSMC își accelerează producția de masă a modulelor CoWoS cu dimensiuni ale substratului depășind 3.000 mm2 pentru a satisface cerințele acceleratoarelor AI generative și ale motoarelor de inferență la scară largă.

Integrarea heterogenă aduce împreună chiplets, stive de memorie și acceleratori specializați — fabricate eventual cu noduri și materiale diferite — într-un singur pachet. Intel Corporation își comercializează tehnologia Foveros Direct, care permite lipirea hibrid la pitch-uri fine pentru stivuirea logică pe logică. Aceasta permite configurații flexibile ale sistemului și optimizarea puterii/performanței la o complexitate giga-scale. Samsung Electronics Co., Ltd. investește de asemenea în platformele X-Cube și I-Cube, vizând AI, memorie de mare lățime de bandă și SoC-uri mobile de generație următoare.

Privind înainte, soluțiile de împachetare giga-scale sunt așteptate să accelereze adopția, stimulată de necesitatea de a integra trilioane de tranzistori în sarcinile de lucru centrate pe date și AI. Consorțiile din industrie, cum ar fi ASE Technology Holding Co., Ltd. lucrează pentru standardizarea interfețelor chiplet, interpozițiilor și rețelelor de livrare a energiei pentru a promova interoperabilitatea ecosistemului. Sectorul anticipează progrese semnificative în fabricarea substratului, gestionarea termică și instrumentele de co-proiectare pentru a sprijini integrarea giga-scale până la sfârșitul decadelor viitoare.

Provocări și Oportunități în Lanțul de Aprovizionare Global

Dezvoltarea rapidă a tehnologiilor de împachetare a circuitelor integrate (IC) giga-scale — cum ar fi IC-urile avansate 2.5D/3D, chiplet și integrarea heterogenă — reconfigurează fundamental dinamica lanțului de aprovizionare global în 2025 și nu doar. Pe măsură ce industria semiconductorilor caută să răspundă cererii crescute pentru calcul de înaltă performanță, acceleratoare AI și rețelistică de generație următoare, complexitatea și scala soluțiilor de împachetare au intensificat atât provocările, cât și oportunitățile de-a lungul lanțului valoric.

O provocare majoră este reziliența lanțului de aprovizionare. Echipamentele, materialele (de exemplu, substraturi de mare densitate, substanțe avansate) și controalele proceselor precise necesare pentru împachetarea giga-scale concentrează riscurile între un mic grup de furnizori. De exemplu, TSMC și Intel au extins ambele capacitatea de împachetare avansată, dar penuria globală de substraturi și disfuncțiile localizate (de exemplu, tensiuni geopolitice, blocaje în logistică) persistă ca preocupări semnificative. Pentru a atenua aceste probleme, jucătorii de frunte investesc în diversificarea geografică și aprovizionarea duală pentru materiale și instrumente critice.

În același timp, tranziția către arhitecturi chiplet și integrarea heterogenă creează noi oportunități pentru colaborarea modulară în lanțul de aprovizionare. Adoptarea chiplet-urilor de către AMD în procesoarele sale EPYC și Ryzen demonstrează cum interfețele standardizate și interconexiunile deschise die-to-die pot permite surse mai flexibile și cicluri de inovație mai rapide. Consorțiile, cum ar fi Universal Chiplet Interconnect Express (UCIe), ai căror membri fondatori includ Intel, AMD, TSMC și Samsung Electronics, încurajează adoptarea soluțiilor interoperabile la nivel de industrie, reducând barierele de intrare pentru noi participanți în ecosistem.

Pe partea de fabricație, investițiile pentru extinderea capacității sunt în derulare. TSMC își accelerează liniile de împachetare avansată CoWoS și SoIC, vizând atât creșterea producției, cât și interconexiuni mai fine pentru a sprijini cipurile AI și HPC. Intel își extinde tehnologiile Foveros Direct și EMIB, iar Samsung Electronics își comercializează platforma de stivuire 3D X-Cube. Aceste mișcări semnalează o competiție globală pentru a obține liderang într-o împachetare giga-scale, necesitănd angajamente semnificative de capital pentru substrat, unealtă și automatizare.

Privind spre următorii câțiva ani, perspectivele pentru soluțiile de împachetare IC giga-scale depind de echilibrarea robustei lanțului de aprovizionare cu viteza de inovație. Standardele de colaborare, investițiile regionale în infrastructura de împachetare avansate și digitalizarea lanțului de aprovizionare (trasabilitate, analize predictive) vor fi cruciale pentru gestionarea riscurilor și captarea oportunităților de piață emergente. Pe măsură ce piețele finale pentru cipuri AI, auto și de centre de date cresc, ecosistemul va vedea probabil o integrare mai strânsă între fabrici, OSAT-uri, furnizori de substraturi și furnizori de instrumente EDA — remodelând limitele tradiționale ale lanțului de aprovizionare pentru semiconductori.

Prezentare Generală a Standardelor Reglementare, de Mediu și Industriale

Evoluția rapidă a soluțiilor de împachetare a circuitelor integrate (IC) giga-scale generează dezvoltări semnificative în standardele reglementare, de mediu și industriale pe măsură ce ne îndreptăm spre 2025 și în a doua jumătate a decadelor. Pe măsură ce complexitatea IC-urilor crește—marcată prin noduri avansate, integrarea sporită a chiplet-urilor și împachetarea heterogenă — organismele de reglementare și consorțiile industriale actualizează cadrele pentru a aborda provocările emergente în siguranță, sustenabilitate și interoperabilitate.

Reglementarea de mediu rămâne un punct focal, procesele de împachetare giga-scale necesitând o atenție mai mare asupra gestionării materialelor și impactului ciclului de viață. Directiva Uniunii Europene privind Restricția Substanțelor Periculoase (RoHS) continuă să modeleze alegerile de materiale, împingând producătorii spre împachetări fără plumb și halogen. Între timp, industria răspunde la Pactul Verde al UE și la strategiile economiei circulare prin inovație în materiale reciclabile pentru substraturi și procese de fabricație cu emisii reduse. De exemplu, Infineon Technologies AG a evidențiat angajamentul său de a reduce impactul ambiental al împachetărilor prin producție eficientă din punct de vedere energetic și utilizarea materialelor reciclate în pachetele IC avansate.

În America de Nord și Asia, alinierea reglementărilor este considerată critică pentru reziliența lanțului de aprovizionare și accesul pe piața globală. Organizații precum SEMI și JEDEC Solid State Technology Association colaborează cu producătorii pentru a armoniza standardele de împachetare, concentrându-se pe fiabilitate, gestionarea termică și performanța electrică pe măsură ce densitățile IC-urilor cresc. Standardele actualizate recent de către JEDEC pentru împachetarea avansată conturează cerințele pentru soluțiile giga-scale, inclusiv dimensiunea substratului, livrarea de putere și integritatea semnalului, asigurând compatibilitate între furnizori și sprijinind creșterea rapidă a ecosistemului.

Industria accelerează, de asemenea, adoptarea cadrelor de sustenabilitate și transparență. Intel Corporation s-a angajat să atingă zero emisii nete de gaze cu efect de seră în întreaga sa operare globală până în 2040, ceea ce include optimizarea proceselor de împachetare și materialele pentru dispozitivele giga-scale. În mod similar, Taiwan Semiconductor Manufacturing Company (TSMC) publică anual rapoarte de sustenabilitate, detaliind reducerile în utilizarea apei și a materialelor chimice în facilitățile sale avansate de împachetare — un factor din ce în ce mai important pe măsură ce soluțiile giga-scale necesită procese mai consumatoare de resurse.

Privind înainte, peisajul reglementării este așteptat să se strângă și mai mult pe măsură ce guvernele și organismele industriale introduc cerințe mai stricte pentru evaluarea ciclului de viață, divulgarea carbonului și siguranța materialelor în împachetarea IC giga-scale. Aceste cadre în evoluție vor modela investițiile și inovația, forțând producătorii să echilibreze cerințele de performanță cu sustenabilitatea și conformitatea pe măsură ce industria se apropie de era exascale.

Previziuni de Piață și Perspective de Investiții până în 2029

Piața pentru soluțiile de împachetare a circuitelor integrate (IC) giga-scale este pregătită pentru o expansiune robustă până în 2029, stimulată de cererea tot mai mare pentru calcul de înaltă performanță, inteligență artificială, centre de date și dispozitive mobile avansate. Împachetarea giga-scale — cuprinzând tehnologii capabile să sprijine miliarde de tranzistori și densitate ultra-înalta I/O — necesită inovații în materiale, design și fabricare, conducând la cheltuieli de capital semnificative și investiții strategice din partea liderilor din industrie.

Începând cu 2025, principalii producători de semiconductori își accelerează rapid capacitățile de împachetare avansată. Taiwan Semiconductor Manufacturing Company (TSMC) a anunțat milestone-uri agresive pe foaia de parcurs pentru tehnologiile sale System-on-Integrated-Chips (SoIC) și 3D Fabric, cu producția în masă a soluțiilor CoWoS avansate și bazate pe chiplet așteptată să se dubleze până în 2026. TSMC investește peste 40 de miliarde de dolari în noi facilități și R&D pentru a sprijini scalarea platformei pentru memorie de mare lățime de bandă (HBM) și acceleratoare AI.

Intel Corporation își accelerează desfășurarea platformei de împachetare 3D Foveros, cu o rată de creștere planificată pentru 2025–2026. Investițiile recente ale companiei — care depășesc 20 de miliarde de dolari pentru noi fabrici și uzine de împachetare din SUA și Europa — sunt menite să asigure un rol de lider în integrarea heterogenă giga-scale și să permită produsele de server, rețelistică și AI de generație următoare.

Samsung Electronics își extinde ofertele X-Cube (integrare 3D) și H-Cube (integrare heterogenă), cu investiții de miliarde de dolari în R&D în domeniul împachetării și liniilor de producție. Samsung preconizează o dublare a cererii pentru soluțiile de împachetare giga-scale în memoria de mare performanță și IC-urile logice până în 2027, subliniind colaborările sale cu furnizorii de servicii de cloud și dezvoltatorii de cipuri AI.

Schimbarea globală către arhitecturi chiplet accelerează în continuare investițiile în fabricarea substraturilor mari și conexiuni avansate. Amkor Technology, unul dintre cei mai importanți furnizori de asamblare și testare semiconductor extern (OSAT), a anunțat noi facilități în Vietnam și Portugalia, vizând ventilarea de mare densitate și împachetarea 2.5D/3D pentru proiectele giga-scale, cu capacitatea operațională planificată să intre în funcțiune până în 2026.

Privind spre 2029, organizațiile din industrie, cum ar fi SEMI, prognozează rate anuale compuse de creștere (CAGR) cu două cifre pentru ambalarea avansată, cu soluții giga-scale constitutive o parte rapid crescătoare a atât pieței totale disponibile, cât și investițiilor de capital. Factorii cheie includ proliferarea sarcinilor de lucru AI, computația exascale și tranziția la noduri de proces sub-2nm, toate necesitând ambalare avansată pentru optimizarea puterii, performanței și factorului de formă.

Analiză Competitivă: Strategiile Companiilor de Vârf (de exemplu, intel.com, tsmc.com, amkor.com)

Concurența globală pentru soluțiile de împachetare a circuitelor integrate (IC) giga-scale se intensifică pe măsură ce producătorii de semiconductori și furnizorii de ambalare avansată își urmăresc inovațiile pentru a răspunde cerințelor de performanță mai ridicate, integrare și eficiență energetică. În 2025 și în viitorul apropiat, liderii din industrie implementează strategii distincte — de la arhitecturi de împachetare proprietare la extinderi strategice de capacitate — pentru a obține cote în piața evolutivă de IC-uri giga-scale.

Intel Corporation își valorifică portofoliul avansat de împachetare, inclusiv tehnologiile Foveros și EMIB (Embedded Multi-die Interconnect Bridge), pentru a permite integrarea de mare densitate și heterogenă a chiplet-urilor pentru centre de date, AI și computere de client. Compania a anunțat recent extinderi pe scară largă ale capacității sale de împachetare avansată în Statele Unite și Europa, cu facilitatile din Ohio așteptându-se să susțină producția avansată de împachetare giga-scale până la mijlocul decadelor. Harta de dezvoltare a Intel pentru 2025 pune accent pe o abordare ”foundry de sistem”, integrând împachetarea avansată ca factor diferențiator în strategia sa IDM 2.0, și colaborează cu parteneri din ecosistem pentru a permite interoperabilitatea deschisă a chiplet-urilor prin standardul UCIe (Universal Chiplet Interconnect Express).

TSMC, principala fabrică de semiconductor, continuă să își extindă platformele sale proprietare CoWoS (Chip-on-Wafer-on-Substrate) și InFO (Integrated Fan-Out), care sunt esențiale pentru IC-urile giga-scale care alimentează calculul de înaltă performanță, rețelistică și acceleratoare AI. În 2025, TSMC își va extinde capacitatea CoWoS, având ca obiectiv dublarea producției pentru a răspunde cererii crescânde din partea hyper-scalers și furnizorilor de cipuri AI. Compania investește, de asemenea, în tehnologia de împachetare de generație următoare, cum ar fi SoIC (System on Integrated Chips), pentru a facilita stivuirea verticală a die-urilor logice și de memorie, sporind astfel densitatea și performanța integrării sistemului. Strategia TSMC se concentrează pe colaborarea strânsă cu clienții pentru a co-optimizeze ambalarea și nodurile de proces, facilitând adoptarea rapidă a arhitecturilor giga-scale.

Amkor Technology, un lider global în asamblarea și testarea semiconductorilor în regim de subcontractare (OSAT), își poziționează competitiv prin creșterea investițiilor în facilități avansate de ambalare la scară mare, în special în Coreea și Vietnam. Portofoliul Amkor include soluții High-Density Fan-Out, 2.5D/3D IC și Silicon Interposer, care sunt din ce în ce mai solicitate pentru aplicații giga-scale în AI, calcul de înaltă performanță și sectorul auto. În 2024, Amkor a inaugurat cea mai mare fabrică de împachetare avansată din Bac Ninh, Vietnam, cu planuri de a-și extinde capacitatea de producție până în 2025 și nu doar Amkor Technology. Strategia Amkor pune accent pe reziliența lanțului de aprovizionare, amprenta globală și parteneriatele tehnologice pentru a livra soluții gama-scale scalabile pentru o bază diversificată de clienți.

Printre acești lideri, perspectivele pentru împachetarea IC giga-scale sunt caracterizate prin investiții agresive în capacitate, colaborări ecosistemice și inovație continuă în arhitecturile de ambalare — poziționând sectorul pentru o creștere robustă pe măsură ce cererea pentru integrarea giga-scale accelerază pe parcursul celei de-a doua jumătăți a decadelor.

Perspective de Viitor: Aplicații Emergente și Tendințe pe Termen Lung

Pe măsură ce industria semiconductorilor avansează spre integrarea giga-scale — unde un singur pachet poate conține zeci de miliarde de tranzistori și o multitudine de componente heterogene — tehnologia de ambalare a devenit un factor crucial pentru inovație. În 2025 și în anii următori, perspectiva pentru soluțiile de împachetare a circuitelor integrate (IC) giga-scale este modelată de cererea în creștere din partea inteligenței artificiale (AI), calculului de înaltă performanță (HPC), rețelisticii avansate și electronicelor de consum de generație următoare.

Una dintre cele mai importante tendințe este maturizarea rapidă și scalarea ambalării avansate 2.5D și 3D, inclusiv arhitecturile chiplet. Aceste abordări permit împărtirea die-urilor mari în chiplets mai mici, prietenoase cu randamentul, care pot fi asamblate pe interpoziții sau substraturi de mare densitate. De exemplu, Intel Corporation își mărește utilizarea tehnologiilor sale EMIB (Embedded Multi-die Interconnect Bridge) și Foveros 3D, facilitând integrarea chiplet-urilor heterogene de calcul, memorie și I/O într-un singur pachet. Taiwan Semiconductor Manufacturing Company (TSMC) continuă să își extindă platformele CoWoS (Chip-on-Wafer-on-Substrate) și SoIC (System on Integrated Chips), susținând stivuirea din ce în ce mai mare a logici-us pe logică și logică pe memorie pentru aplicații de centre de date și acceleratoare AI.

Perspectivele pentru 2025 și dincolo leagă soluțiile de împachetare giga-scale nu doar de densitate și integrare, ci și de gestionarea puterii, gestionarea termică și provocările de integritate a semnalului. Advanced Micro Devices, Inc. (AMD) și NVIDIA Corporation explorează activ soluții avansate de GPU multi-die și acceleratoare, valorificând interconexiuni de mare lățime de bandă și materiale inovatoare de substrat pentru a satisface nevoile generative AI și ale calculului de mare viteză.

Aplicațiile emergente, cum ar fi AI la margine, comunicațiile 6G și autonomia auto, promovează și mai mult necesitatea ambalării giga-scale. Sectorul auto, de exemplu, necesită pachete IC de înaltă fiabilitate, eficiență termică și miniaturalizate pentru fuzionarea senzorilor și inferența în timp real, o nevoie care este abordată de furnizori precum Infineon Technologies AG și Renesas Electronics Corporation.

Privind înainte, foile de parcurs din industrie anticipează continuarea scalării pitch-urilor de micro-bump și lipirea hibrid, adoptarea substraturilor cu miez de sticlă pentru integritatea extremă a semnalului și proliferarea automatizării proiectării ghidate de AI pentru aranjamente complexe de ambalare. Eforturile de standardizare și colaborările ecosistemice — cum ar fi inițiativa Universal Chiplet Interconnect Express (UCIe) — sunt așteptate să accelereze interoperabilitatea și creșterea ecosistemului (Consorțiu Universal Chiplet Interconnect Express).

În concluzie, soluțiile de ambalare IC giga-scale în 2025 și dincolo vor fi factori fundamentali în facilitarea calculului, comunicațiilor și sistemelor inteligente de margine de generație următoare, cu inovații concentrate pe densitate, integrare și performanța holistică a sistemului.

Surse & Referințe

- Amkor Technology

- JEDEC

- ASE Technology Holding

- IBIDEN Co., Ltd.

- SHINKO ELECTRIC INDUSTRIES CO., LTD.

- Infineon Technologies AG

- Amkor Technology

- NVIDIA Corporation

- Universal Chiplet Interconnect Express Consortium